Distributed by:

# www.Jameco.com + 1-800-831-4242

The content and copyrights of the attached material are the property of its owner.

## **Jameco Part Number 48910**

## DM74S571 (512 x 4) 2048-Bit TTL PROM

## **General Description**

This Schottky memory is organized in the popular 512 words by 4 bits configuration. A memory enable input is provided to control the output states. When the device is enabled, the outputs represent the contents of the selected word. When disabled, the 4 outputs go to the "OFF" or high impedance state.

PROMs are shipped from the factory with lows in all locations. A high may be programmed into any selected location by following the programming instructions.

### **Features**

- Advanced titanium-tungsten (Ti-W) fuses

- Schottky-clamped for high speed Address access down to—35 ns max Enable access—25 ns max Enable recovery—25 ns max

- PNP inputs for reduced input loading

- All DC and AC parameters guaranteed over temperature

- Low voltage TRI-SAFE™ programming

- TRI-STATE® outputs

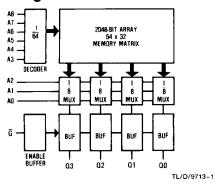

## **Block Diagram**

### Pin Names

| A0-A8 | Address       |

|-------|---------------|

| G     | Output Enable |

| GND   | Ground        |

| Q0-Q3 | Outputs       |

| Vcc   | Power Supply  |

TL/D/9713-3

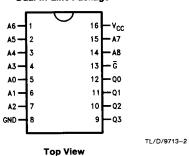

## **Connection Diagrams**

### **Dual-In-Line Package**

**Order Number** DM74S571J, 571AJ, 571BJ DM74S571N, 571AN, 571BN See NS Package Number J16A or N16A

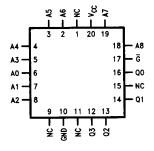

### Plastic Leaded Chip Carrier (PLCC)

**Top View**

**Order Number** DM74S571V, 571AV, 571BV See NS Package Number V20A

## **Ordering Information**

Commercial Temperature Range (0°C to +70°C)

| Parameter/Order Number | Max Access Time (ns) |

|------------------------|----------------------|

| DM74S571AN             | 45                   |

| DM74S571BN             | 35                   |

| DM74S571N              | 55                   |

| DM74S571AJ             | 45                   |

| DM74S571BJ             | 35                   |

| DM74S571J              | 55                   |

| DM74S571AV             | 45                   |

| DM74S571BV             | 35                   |

| DM74S571V              | 55                   |

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage (Note 2) -0.5V to +7.0V -1.2V to +5.5V

Output Voltage (Note 2)

-0.5V to +5.5V

Storage Temperature

-65°C to +150°C

Lead Temp. (Soldering 10 sec.) 300°C

ESD to be determined

Note 1: Absolute maximum ratings are those values beyond which the device may be permanently damaged. They do not mean that the device may be operated at these values.

Note 2: These limits do not apply during programming. For the programming ratings, refer to the programming instructions.

| Operating Conditions                             |      |      |       |  |  |  |  |  |  |

|--------------------------------------------------|------|------|-------|--|--|--|--|--|--|

|                                                  | Min  | Max  | Units |  |  |  |  |  |  |

| Supply Voltage (V <sub>CC</sub> )<br>Commercial  | 4.75 | 5.25 | V     |  |  |  |  |  |  |

| Ambient Temperature (T <sub>A</sub> ) Commercial | 0    | +70  | °C    |  |  |  |  |  |  |

| Logical "0" Input Voltage                        | 0    | 0.8  | V     |  |  |  |  |  |  |

| Logical "1" Input Voltage                        | 2.0  | 5.5  | V     |  |  |  |  |  |  |

## DC Electrical Characteristics (Note 1)

| Symbol          | Parameter                       | Conditions                                                                     |     | Unit |      |            |

|-----------------|---------------------------------|--------------------------------------------------------------------------------|-----|------|------|------------|

|                 |                                 | 30114.113.13                                                                   | Min | Тур  | Max  | 1          |

| կլ              | Input Load Current              | V <sub>CC</sub> = Max, V <sub>IN</sub> = 0.45V                                 |     | -80  | -250 | μΑ         |

| hн              | Input Leakage Current           | $V_{CC} = Max, V_{IN} = 2.7V$                                                  |     |      | 25   | μА         |

| ············    |                                 | $V_{CC} = Max, V_{IN} = 5.5V$                                                  |     |      | 1.0  | mA         |

| V <sub>OL</sub> | Low Level Output Voltage        | V <sub>CC</sub> = Min, I <sub>OL</sub> = 16 mA                                 |     | 0.35 | 0.45 | V          |

| V <sub>IL</sub> | Low Level Input Voltage         |                                                                                |     |      | 0.80 | V          |

| V <sub>IH</sub> | High Level Input Voltage        |                                                                                | 2.0 |      |      | V          |

| V <sub>C</sub>  | Input Clamp Voltage             | $V_{CC} = Min, I_{IN} = -18 \text{ mA}$                                        |     | -0.8 | -1.2 | V          |

| Cı              | Input Capacitance               | $V_{CC} = 5.0V, V_{IN} = 2.0V$<br>$T_A = 25^{\circ}C, 1 \text{ MHz}$           |     | 4.0  |      | pF         |

| C <sub>O</sub>  | Output Capacitance              | $V_{CC} = 5.0V$ , $V_{O} = 2.0V$<br>$T_{A} = 25^{\circ}C$ , 1 MHz, Outputs Off |     | 6.0  |      | pF         |

| lcc             | Power Supply Current            | V <sub>CC</sub> = Max, input Grounded<br>All Outputs Open                      |     | 90   | 130  | m <i>A</i> |

| los             | Short Circuit<br>Output Current | V <sub>O</sub> = 0V, V <sub>CC</sub> = Max<br>(Note 2)                         | -20 |      | -70  | mA         |

| loz             | Output Leakage                  | $V_{CC} = Max, V_{O} = 0.45V \text{ to } 2.4V$                                 |     |      | + 50 | μА         |

|                 | (TRI-STATE)                     | Chip Disabled                                                                  |     |      | -50  | μА         |

| V <sub>OH</sub> | Output Voltage High             | $I_{OH} = -2.0 \text{ mA}$                                                     |     |      |      | V          |

| ļ               | 1                               | $I_{OH} = -6.5 \text{ mA}$                                                     | 2.4 | 3.2  |      | V          |

Note 1: These limits apply over the entire operating range unless stated otherwise. All typical values are for  $V_{CC}=5.0V$  and  $T_A=25^{\circ}C$ .

Note 2: During IOS measurement, only one output at a time should be grounded. Permanent damage may otherwise result.

### **AC Electrical Characteristics**

COMMERCIAL TEMP RANGE (0°C to +70°C)

| Symbol | JEDEC  | Parameter            | DM74S571 |     | DM74S571A |     |     | DM74S571B |     |     | Unit |    |

|--------|--------|----------------------|----------|-----|-----------|-----|-----|-----------|-----|-----|------|----|

|        | Symbol |                      | Min      | Тур | Max       | Min | Тур | Max       | Min | Тур | Max  | J  |

| TAA    | TAVQV  | Address Access Time  |          | 40  | 55        |     | 30  | 45        |     | 30  | 35   | ns |

| TEA    | TEVQV  | Enable Access Time   |          | 20  | 30        |     | 15  | 25        |     | 15  | 25   | ns |

| TER    | TEXQX  | Enable Recovery Time |          | 20  | 30        |     | 15  | 25        |     | 15  | 25   | ns |

| TZX    | TEVQX  | Output Enable Time   |          | 20  | 30        |     | 15  | 25        |     | 15  | 25   | ns |

| TXZ    | TEXQZ  | Output Disable Time  |          | 20  | 30        |     | 15  | 25        |     | 15  | 25   | ns |

## **Functional Description**

### **TESTABILITY**

The Schottky PROM die includes extra rows and columns of fusable links for testing the programmability of each chip. These test fuses are placed at the worst-case chip locations to provide the highest possible confidence in the programming tests in the final product. A ROM pattern is also permanently fixed in the additional circuitry and coded to provide a parity check of input address levels. These and other test circuits are used to test for correct operation of the row and column-select circuits and functionality of input and enable gates. All test circuits are available at both wafer and assembled device levels to allow 100% functional and parametric testing at every stage of the test flow.

### RELIABILITY

As with all National products, the Ti-W PROMs are subjected to an on-going reliability evaluation by the Reliability Assurance Department. These evaluations employ accelerated life tests, including dynamic high-temperature operating life, temperature-humidity life, temperature cycling, and thermal shock. To date, nearly 7.4 million Schottky Ti-W PROM device hours have been logged, with samples in Epoxy B molded DIP (N-package), PLCC (V-package) and CERDIP (J-package). Device performance in all package configurations is excellent.

### **TITANIUM-TUNGSTEN FUSES**

National's Programmable Read-Only Memories (PROMs) feature titanium-tungsten (Ti-W) fuse links designed to program efficiently with only 10.5V applied. The high performance and reliability of these PROMs are the result of fabrication by a Schottky bipolar process, of which the titanium-tungsten metallization is an integral part, and the use of an on-chip programming circuit.

A major advantage of the titanium-tungsten fuse technology is the low programming voltage of the fuse links. At 10.5V, this virtually eliminates the need for guard-ring devices and wide spacings required for other fuse technologies. Care is taken, however, to minimize voltage drops across the die and to reduce parasitics. The device is designed to ensure that worst-case fuse operating current is low enough for reliable long-term operation. The Darlington programming circuit is liberally designed to insure adequate power density for blowing the fuse links. The complete circuit design is optimized to provide high performance over the entire operating ranges of V<sub>CC</sub> and temperature.